Содержание

Bolt Graphics завершила tape-out тестового чипа Zeus GPU на техпроцессе TSMC 12nm FFC. Компания говорит о цели в 17 раз снизить стоимость вычислений и впервые переходит от FPGA-эмуляции к кремнию.

Мы смотрим на новость через призму «что точно известно, а что пока шум». У Bolt до этого были громкие цифры, но без рабочего чипа. Tape-out — первый момент, где обещания начинают упираться в физику и производство.

От FPGA к кремнию: что Bolt подтверждает железом

Факт номер один: у Zeus теперь есть тестовый чип, спроектированный под TSMC 12nm FFC (часть зрелого семейства 16/12-нм FinFET). Это важнее любых слайдов. На этом этапе компания сможет дать заказчикам не «модель», а реальные замеры на кремнии.

Bolt пишет, что архитектура Zeus работала на FPGA и её оценивали клиенты четыре года. Теперь тестовый чип пойдёт в customer benchmarking, а целевой старт поставок в продакшене компания привязывает к Q4 2027.

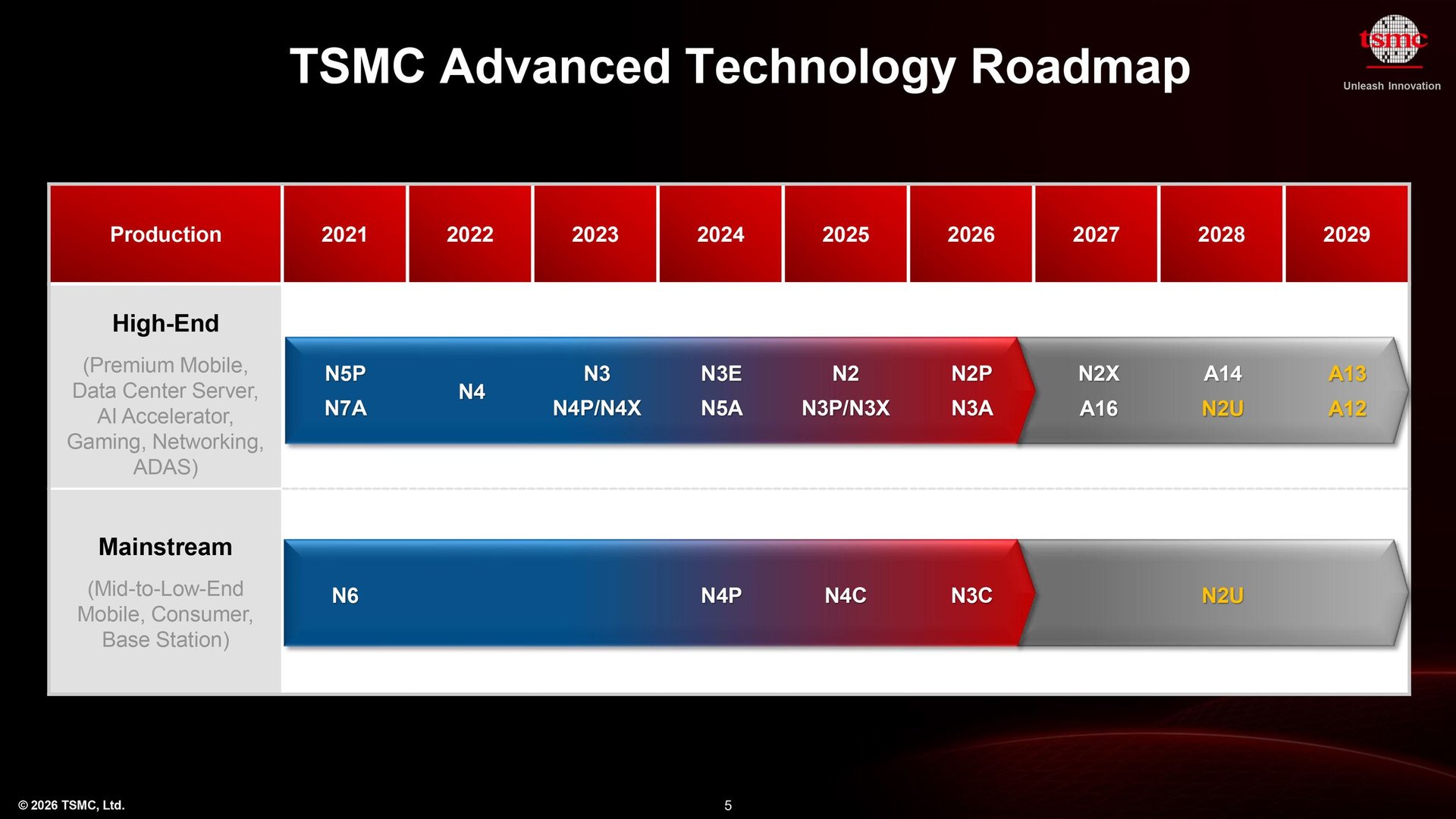

При этом 12 нм здесь выглядит как шаг валидации. Bolt отдельно подчёркивает, что Zeus проектировали и под «advanced nodes, включая 5 нм». То есть финальный продукт компания может увести на более тонкий техпроцесс, но подтверждения этого пока нет.

Где обещания самые смелые, и почему к ним есть вопросы

Самое громкое заявление Bolt из начала 2025 года: Zeus якобы выдаст до 10 раз больше пропускной способности в path tracing, чем Nvidia GeForce RTX 5090. Тогда это опиралось на внутренние симуляции и FPGA-тесты, а не на чип в руках.

С tape-out компания впервые получает шанс показать, как эти оценки соотносятся с реальностью. Но важно разделять: тестовый чип на 12 нм — не гарантия, что финальные карты будут на том же узле и с теми же частотами, энергопотреблением и выходом годных кристаллов.

Bolt также называет целевые рынки, где «не хватает доступных вычислений»: HPC, электромагнитное моделирование и рендеринг. Совокупный объём этих рынков компания оценивает в $55 млрд.

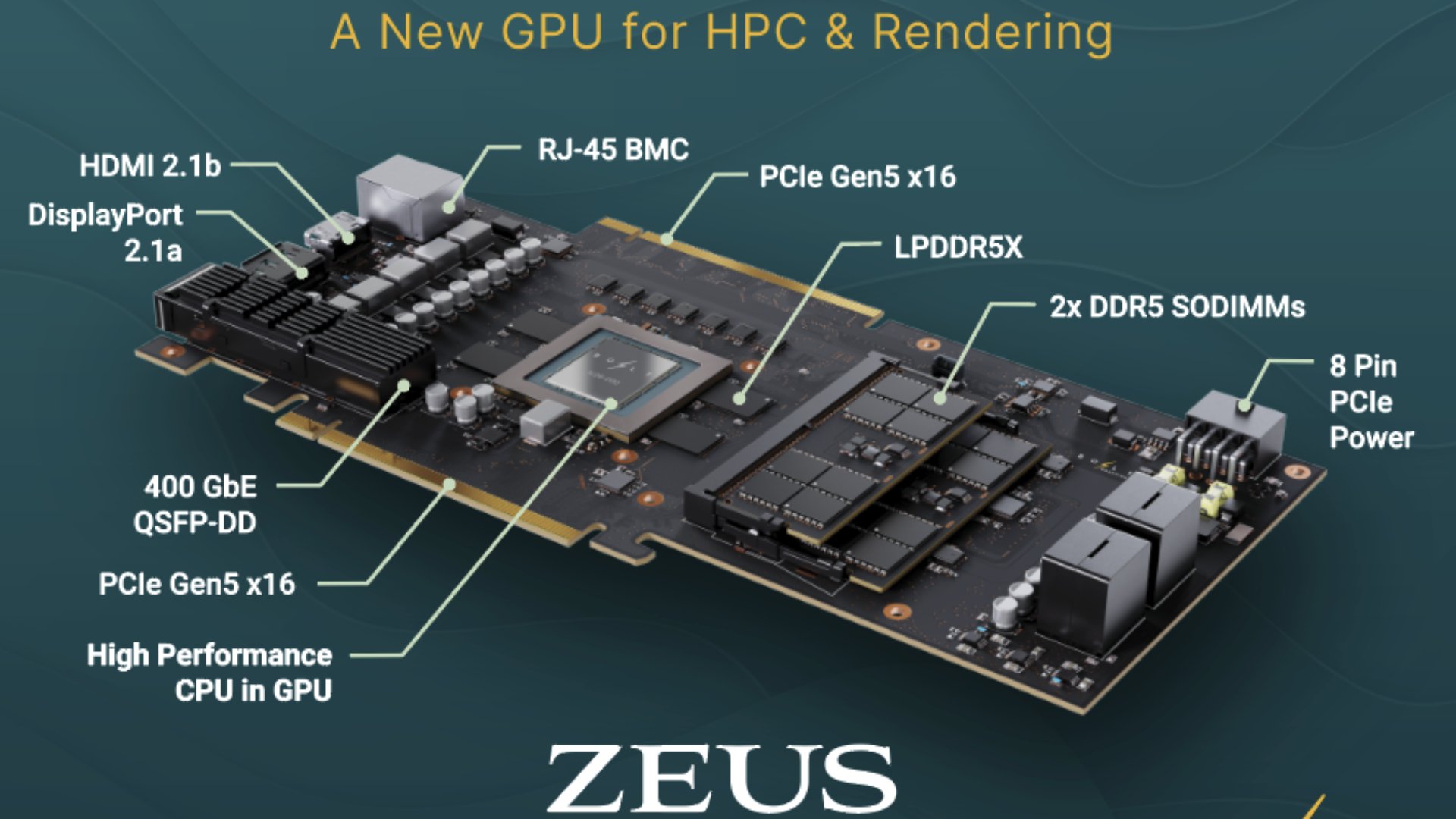

Заявленные характеристики карт Zeus: питание, TFLOPS, память и 400 GbE

По спецификациям, Zeus планируют в формате PCIe-карт и 2U-серверов. В линейке заявлены однослотовые и двухслотовые варианты с питанием 120 Вт и 250 Вт, крупным on-chip cache и необычной для GPU схемой памяти: смесь LPDDR5X на плате и сменных DDR5 SO-DIMM.

| Модель | Форм-фактор | Питание | FP64/FP32/FP16 (TFLOPS) | INT16/INT8 matrix (TFLOPS) | Кэш на кристалле | Память | Сеть |

|---|---|---|---|---|---|---|---|

| Bolt Zeus 1c26-032 | Single-slot PCIe | 120 W | 5 / 10 / 20 | 307.2 / 614.4 | 128 MB | До 160 GB (32 GB LPDDR5X + 2x DDR5 SO-DIMM) | 400 GbE |

| Bolt Zeus 2c26-064 | Dual-slot PCIe | 250 W | 10 / 20 / 40 | 614.4 / 1,228.8 | 256 MB | До 320 GB (64 GB LPDDR5X + 4x DDR5 SO-DIMM) | 400 GbE |

| Bolt Zeus 2×26-128 | Dual-slot PCIe | 250 W | 10 / 20 / 40 | 614.4 / 1,228.8 | 256 MB | До 384 GB (128 GB LPDDR5X + 4x DDR5 SO-DIMM) | 400 GbE |

Выглядит не как «ещё один ускоритель», а как попытка сделать карту под задачи, где упираются в память и сеть. Но пока это всё спецификации на бумаге. Реальные бенчмарки на тестовом чипе и итоговая конфигурация продакшен-карт — ключевые неизвестные.

Деньги, интерес рынка и сдвиг сроков

Bolt заявляет, что её продуктовый пайплайн превышает $500 млн. Ещё компания говорит, что в early access записались более 14 000 предприятий, разработчиков и конечных пользователей.

Series A, по словам Bolt, подписали с переподпиской на 50%, но сумму и лид-инвесторов компания не раскрыла. По срокам тоже есть сдвиг: раньше Bolt ориентировалась на dev kits в конце 2025 года и производство в конце 2026-го. На CES в январе компания показывала прототип карты, но рабочего кремния тогда не было.

Теперь Bolt привязывает производство к Q4 2027 и прямо говорит, что тестовый чип нужен для бенчмарков у клиентов перед этим этапом.

По тестовому чипу Zeus на TSMC 12nm FFC компания планирует клиентские замеры уже перед подготовкой к производственному разгону, а целевой срок продакшена — четвёртый квартал 2027 года.