Содержание

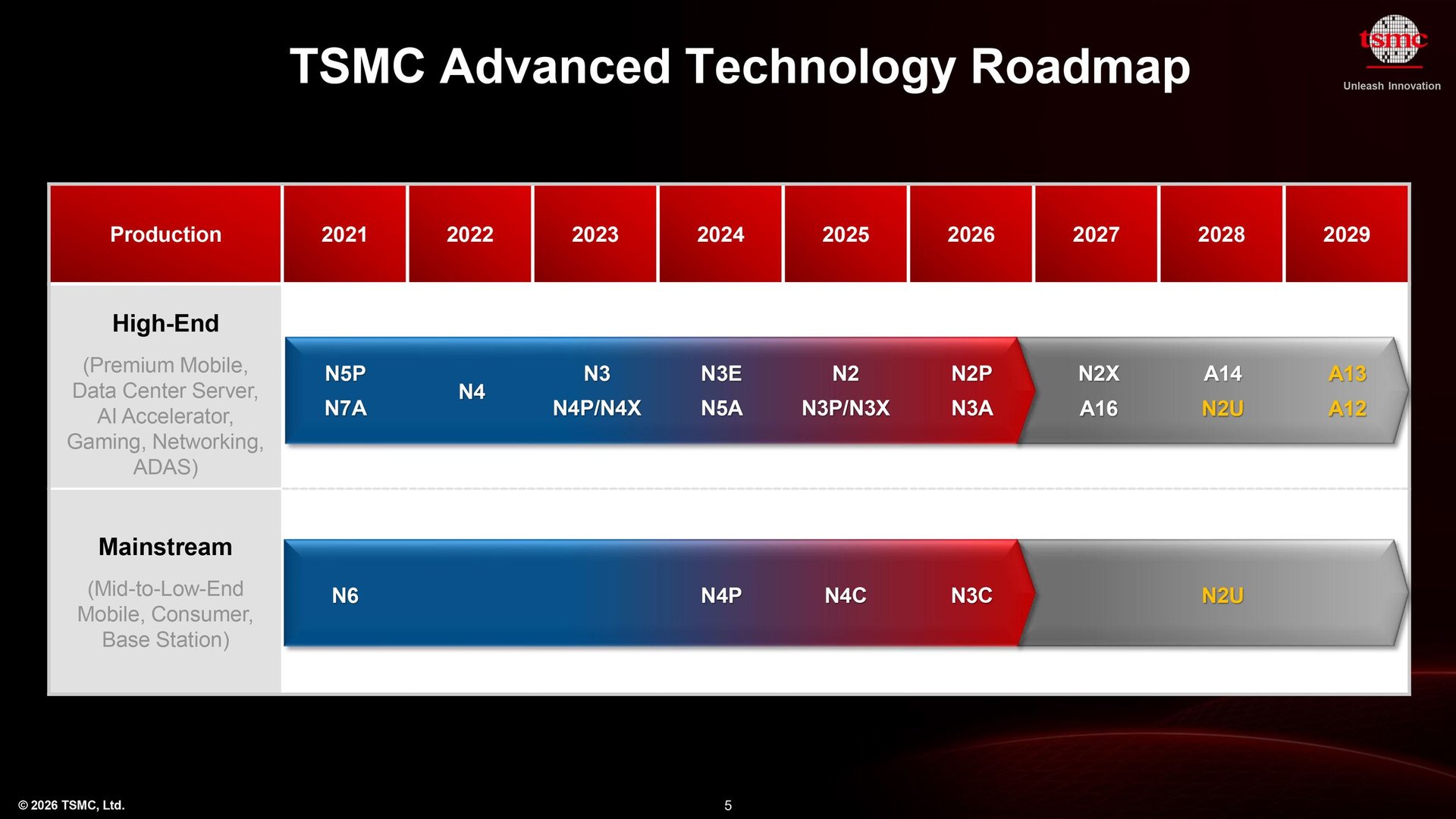

TSMC на своём North American Technology Symposium 2026 показала общую дорожную карту техпроцессов до 2029 года. В ней появились 1,2-нм и 1,3-нм классы A12 и A13, неожиданное расширение семейства 2 нм под названием N2U, а ещё компания подтвердила: через 2029 год она не планирует переходить на High-NA EUV.

Отдельно TSMC уточнила сроки по A16. Технология будет «готова для производства» в 2026-м, но массовый выпуск (volume production) компания теперь привязала к 2027 году.

TSMC разделила передовые узлы на «клиентские» и «серверные»

Ключевой сдвиг в логике roadmap — TSMC больше не пытается вести один «универсальный» передовой узел для всех. Компания прямо разделила стратегию по рынкам: для смартфонов и клиентских устройств она хочет обновлять узлы ежегодно, а для AI и HPC — раз в два года, но с более ощутимым приростом.

По словам Кевина Чжана (Kevin Zhang), старшего вице-президента по развитию бизнеса, глобальным продажам и заместителя COO, TSMC продолжит выпускать «новый узел для client каждый год» и «новый узел для тяжёлых AI/HPC задач каждые два года».

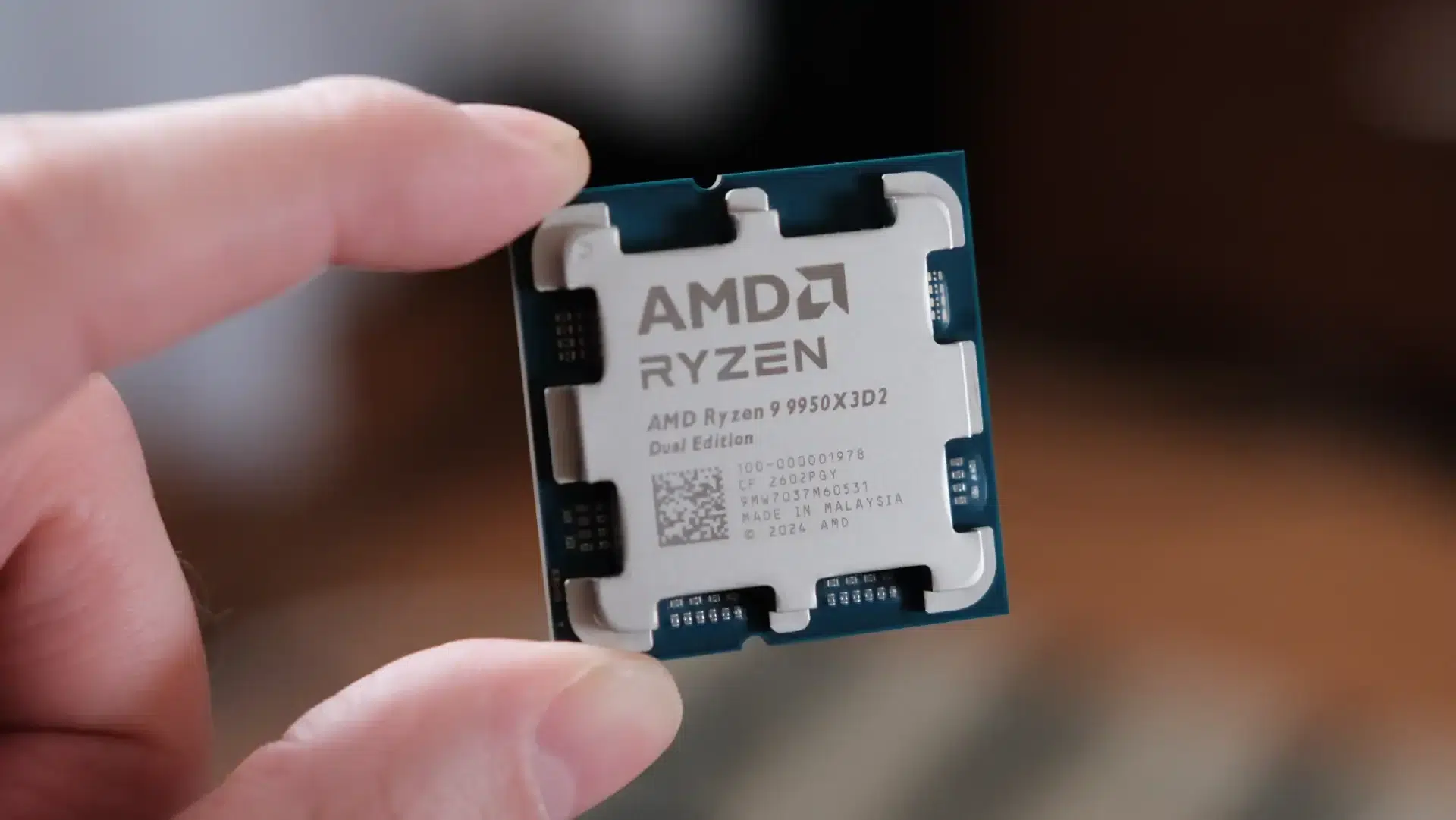

- Client-ветка: N2, N2P, N2U, A14, A13 — упор на стоимость, энергоэффективность и совместимость по IP.

- AI/HPC-ветка: A16 и A12 — упор на максимальную производительность, а стоимость вторична.

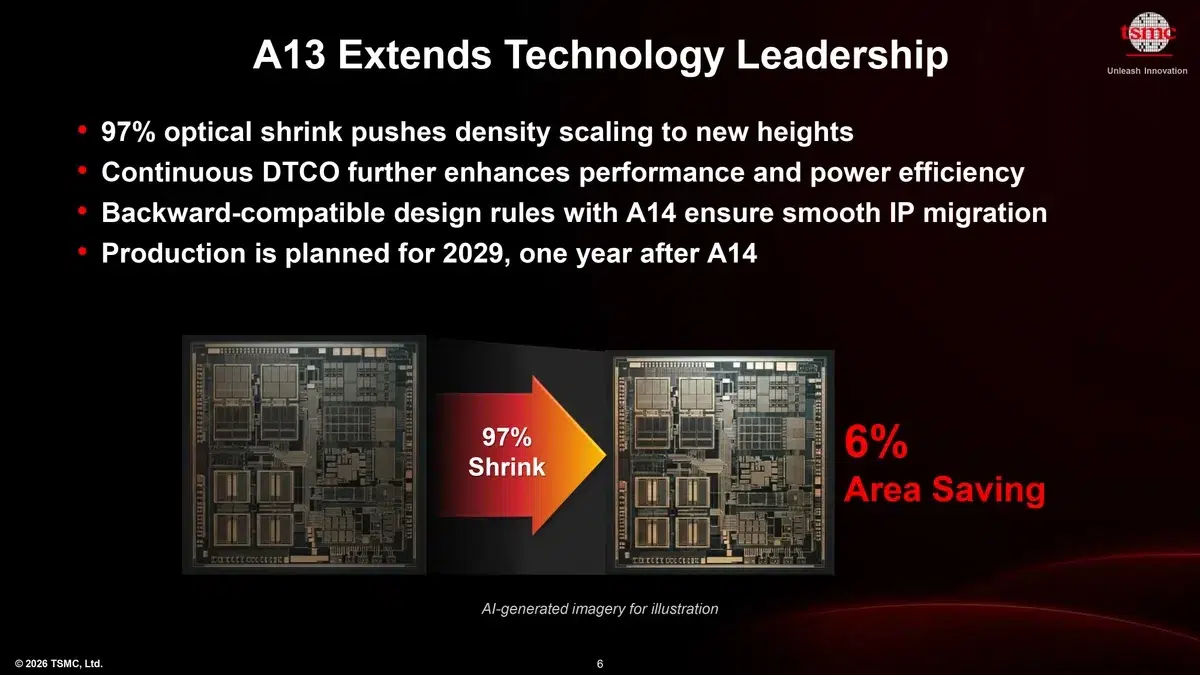

A13 и N2U: апгрейд с минимальным редизайном

A14 TSMC анонсировала годом ранее как свою «2nd Generation nanosheet» технологию, рассчитанную на премиальные смартфоны и клиентские чипы, с планом производства в 2028 году. Теперь компания добавила производные: A13 и A12, обе запланированы на 2029 год.

A13 TSMC описывает как инкрементальное улучшение A14 за счёт optical shrink. Компания говорит о снижении линейных размеров примерно на 3% (масштаб до ~97%), что даёт около 6% прироста плотности. При этом A13 сохраняет полную совместимость с A14 по design rules и электрическим параметрам, то есть переход должен пройти с минимальными переделками.

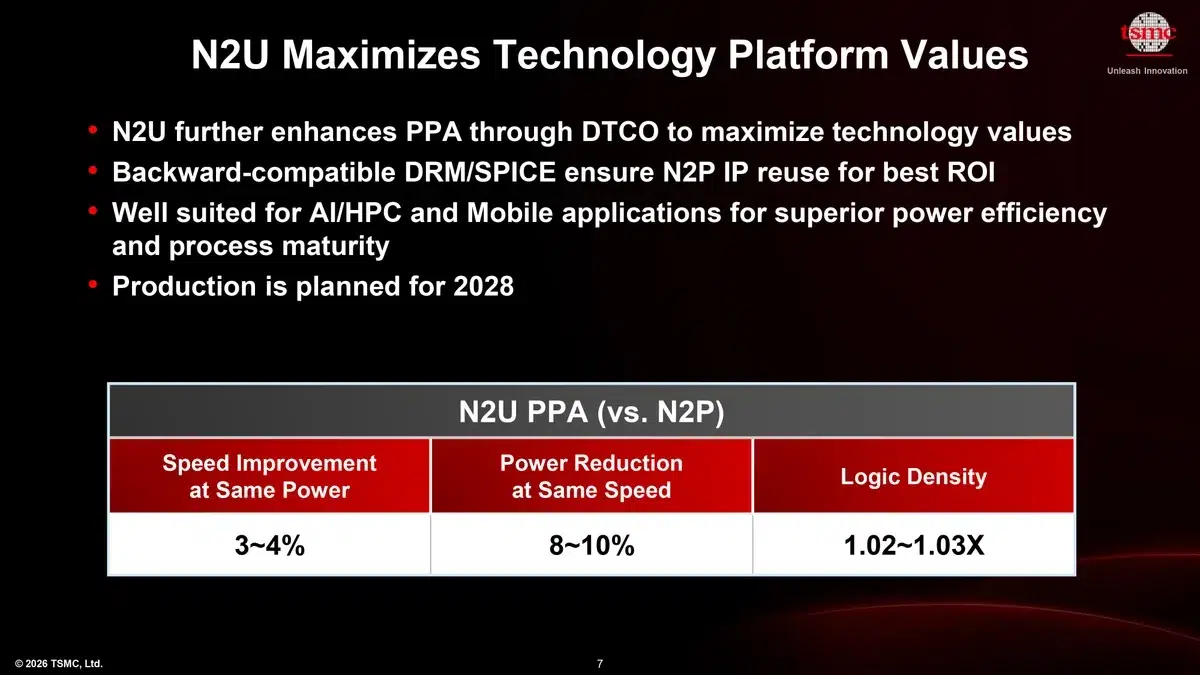

Второй «дешёвый» апгрейд — N2U, третьегодичное расширение 2-нм платформы. Он нацелен на тех, кто хочет выжать ещё немного PPA из дизайнов на базе N2, не уходя в полностью новый узел.

- N2U vs N2P (производительность): +3% — +4% при той же мощности.

- N2U vs N2P (энергопотребление): -8% — -10% при той же скорости.

- N2U (плотность логики): +2% — +3%.

- Совместимость: N2U сохраняет совместимость с IP для N2P.

Кевин Чжан прямо объяснил смысл таких «продлений»: компания хочет улучшать узлы после их запуска, чтобы заказчики «максимизировали отдачу от инвестиций в дизайн» и при этом получали инкрементальные PPA-бонусы.

A16 и A12: ставка на backside power, а не на High-NA EUV

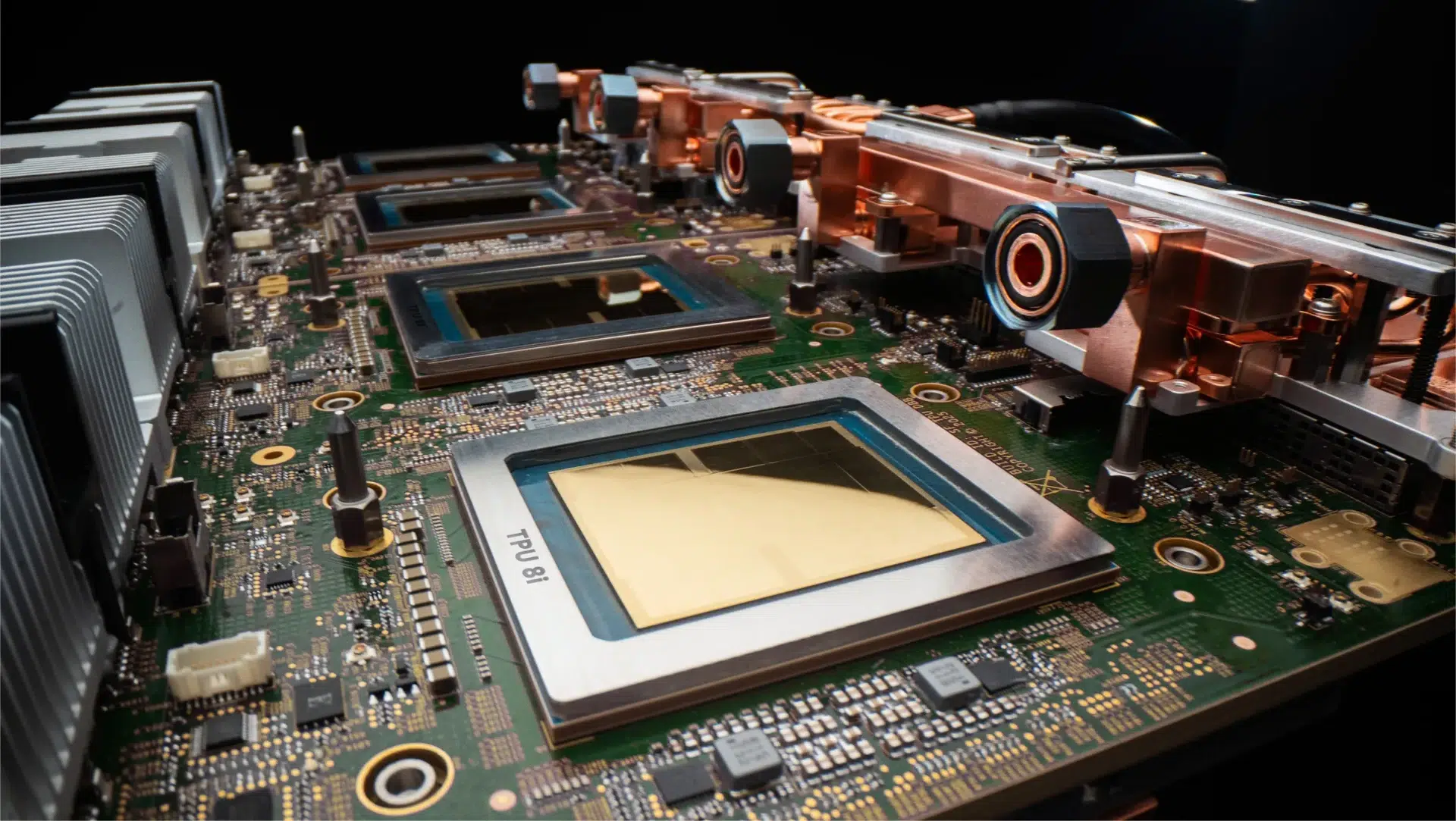

Для дата-центрового сегмента TSMC делает отдельную линию, где ключевая фишка — Super Power Rail (SPR), то есть подвод питания с обратной стороны кристалла (backside power delivery). Именно этим A16 отличается от N2P: по сути, это N2P с SPR и с 1-м поколением nanosheet GAA.

TSMC приводит ориентиры по сравнению A16 vs N2P: снижение потребления на 15% — 20%, рост производительности на 8% — 10% и рост «смешанной» плотности чипа на 1,07x — 1,10x (метрика TSMC для 50% логики, 30% SRAM и 20% аналоговых блоков).

По срокам A16 компания дала важную оговорку. «A16 will be ready for production in 2026», — сказал Чжан. Но реальный ramp зависит от клиентов, и поэтому TSMC ждёт volume production в 2027 году и «выровняла» таймлайн под это.

При этом N2X никуда не девается. Это performance-вариант N2P с традиционным front-side power delivery, который нацелен на максимальные частоты без перехода на backside power.

Следующий шаг для AI/HPC — A12 с планом HVM в 2029 году. TSMC не раскрыла точные цифры, но описывает A12 как «следующее поколение» SPR по сравнению с A16 и связывает его с геометрическим масштабированием, где нужно синхронно уменьшать и frontside, и backside геометрию.

High-NA EUV до 2029 года TSMC не закладывает

Самый нетипичный момент в roadmap — TSMC не планирует использовать High-NA EUV ни для одного узла до 2029 года, включая A13 и A12. Кевин Чжан объяснил это прямым текстом: команда R&D «продолжает находить способ масштабироваться без High-NA», а переход на High-NA компания считает крайне дорогим.

На этом фоне подход TSMC отличается от Intel, которая собирается применять High-NA EUV, начиная с узла 14A и последующих, с ориентиром на 2027-2028 годы.

По плану TSMC, A13 и A12 должны выйти в производство в 2029 году, а A16 компания теперь привязала к массовому выпуску в 2027-м.