Содержание

Rambus 5 марта 2026 года объявила о новом IP для контроллера HBM4E. Компания заявляет скорость до 16 Гбит/с на пин и пропускную способность до 4,1 ТБ/с на один стек памяти — цифры, которые в первую очередь целятся в будущие AI-ускорители и GPU.

Речь не о готовой памяти и не о видеокарте. Это лицензируемая «начинка» для чипов: контроллер, который производители SoC и базовых кристаллов могут встроить в свои проекты.

Какие цифры заявляет Rambus для HBM4E

Ключевой параметр в анонсе — скорость интерфейса: до 16 Гбит/с на контакт. Rambus привязывает к этому и итоговую пропускную способность: до 4,1 ТБ/с на один HBM4E-стек (в релизе это названо «to each memory device»).

Если собрать типичную для ускорителей конфигурацию с несколькими стеками, масштабирование выглядит так. Для AI-ускорителя с восемью подключёнными HBM4E-устройствами Rambus заявляет более 32 ТБ/с общей пропускной способности памяти.

- Скорость: до 16 Гбит/с на пин

- Пропускная способность на стек: до 4,1 ТБ/с

- Пример для 8 стеков: более 32 ТБ/с

Как это будут внедрять: 2.5D/3D и отдельный PHY

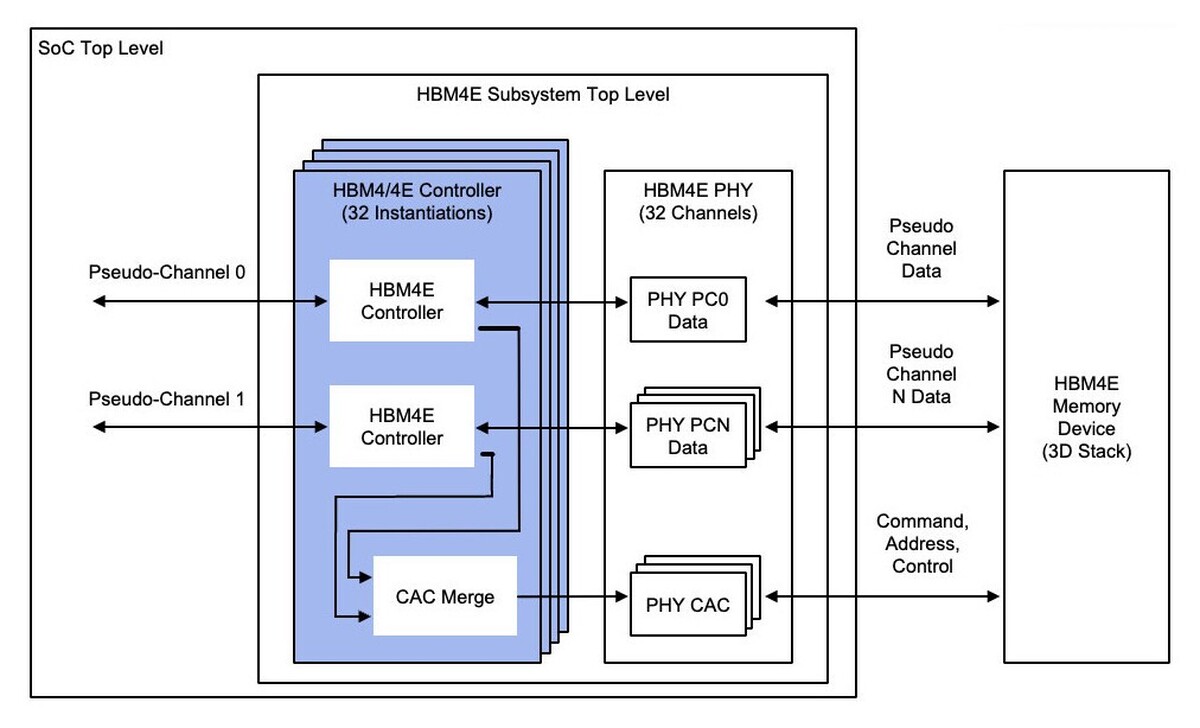

Rambus подчёркивает, что её HBM4E Controller IP можно сочетать с «third-party standard or TSV PHY solutions». По сути, компания продаёт цифровую часть контроллера, а физический уровень (PHY) можно взять у сторонних поставщиков, чтобы собрать полный HBM4E-подсистемный блок.

Целевые варианты упаковки названы напрямую: 2.5D или 3D package. Это тот самый мир интерпозеров и стеков, где живут современные AI-ускорители и HPC-чипы, а память сидит рядом с вычислительным кристаллом.

Ещё один важный момент из формулировок Rambus: контроллер рассчитан не только на «AI accelerators», но и на graphics и HPC applications. То есть компания явно держит в голове и будущие профессиональные GPU, где HBM традиционно встречается чаще, чем в массовом гейминге.

Почему упор именно на AI: память стала узким местом

В анонсе Rambus прямо говорит про «insatiable bandwidth demands of AI». И это не маркетинговая поэзия, а понятная боль индустрии: у больших моделей и плотных матричных вычислений память и её пропускная способность часто упираются раньше, чем «сырой» compute.

Simon Blake-Wilson, SVP и general manager Silicon IP в Rambus, формулирует это так: «Given the insatiable bandwidth demands of AI, it’s imperative for the memory ecosystem to continue aggressively advancing memory performance». В переводе на нормальный инженерный: если не гнать bandwidth, ускорители будут простаивать.

Похожую мысль озвучил и Reiner Pope, co-founder и CEO MatX: «HBM bandwidth is one of the main bottlenecks on LLM performance». То есть речь именно про LLM-нагрузки, где движение данных критично.

Samsung тоже публично поддержала тему. Ben Rhew, corporate vice president и head of the Foundry IP Development Team в Samsung Electronics, называет HBM4E «significant milestone» и добавляет, что IP-решения для HBM4E будут «essential for broad industry adoption».

Rambus уточняет статус продукта: HBM4E Controller IP уже доступен для лицензирования, а ранние заказчики могут подключаться к early access «сегодня».

Источники: Rambus, Samsung Electronics

Страница Rambus по HBM Interface IP