Содержание

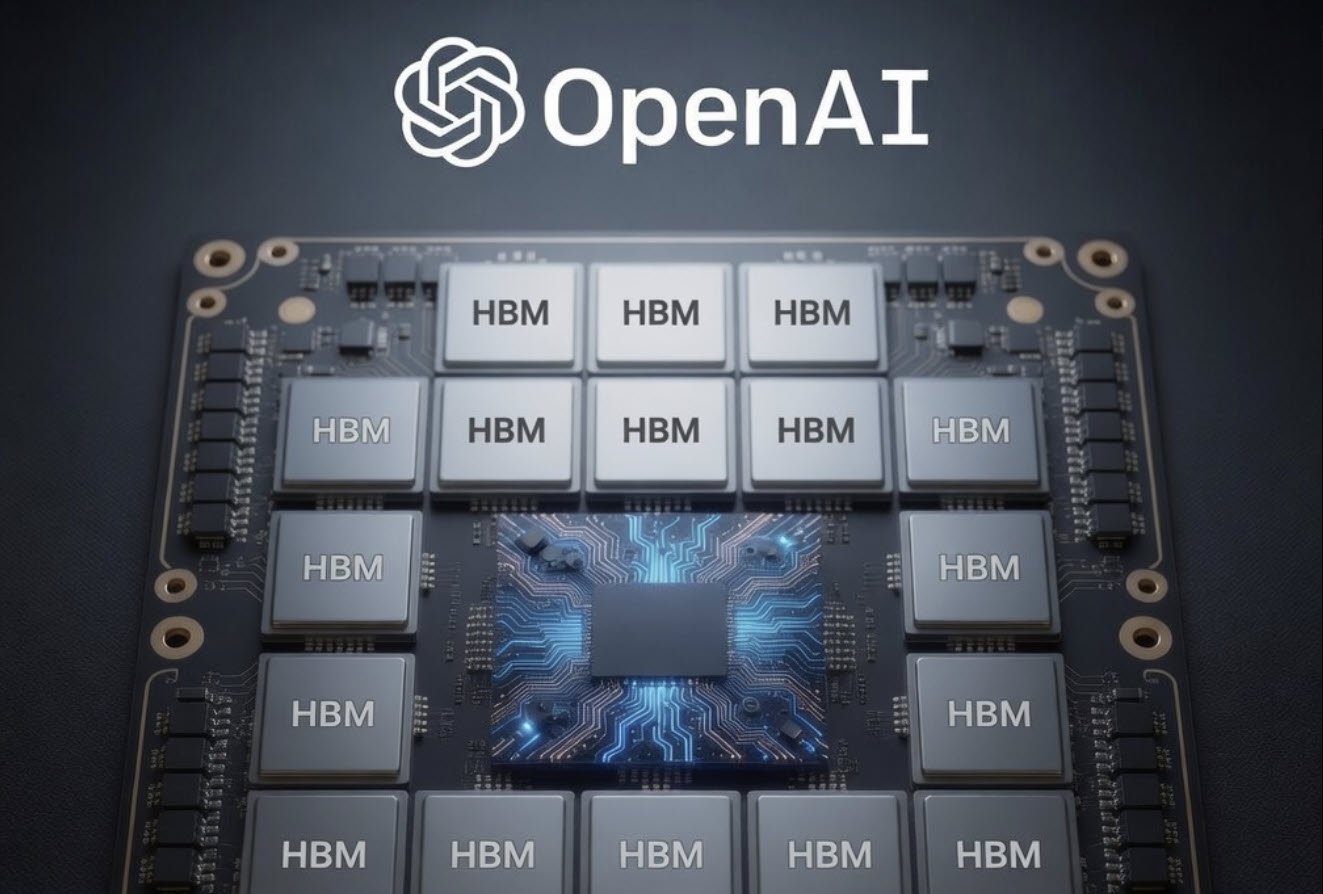

В патенте OpenAI описала концепт собственного AI-чипа: несколько вычислительных чиплетов и до 20 стеков HBM вокруг них. Ключевой элемент — Embedded Logic Bridges, которые должны снять ограничения по расстоянию между HBM и вычислительным кристаллом.

Речь не про готовый продукт и не про анонс. Это патентная заявка с архитектурной идеей, как упаковать больше памяти рядом с вычислением и не упереться в физику проводников на подложке.

Зачем OpenAI уходит от «HBM только рядом с чипом»

Проблема, которую описывает OpenAI, упирается в текущие правила компоновки HBM в 2.5D-упаковке. По JEDEC стек HBM должен стоять рядом с вычислительным чиплетом, потому что связь идёт по металлическим линиям на базовом слое, а длина этих линий ограничена.

В патенте приводится конкретная цифра: стандартный подход требует держать проводники короче 6 мм от PHY-контроллера на основном чиплете. Из-за этого производители обычно ограничиваются четырьмя, шестью или восьмью HBM-стеками на одном пакете. Дальше начинает мешать геометрия.

Embedded Logic Bridges: 16 мм вместо 6 мм и совместимость с UCIe

OpenAI предлагает использовать embedded logic bridges (в патенте — Embedded Logic Bridges). Они должны «дотянуть» связь между чиплетами и HBM дальше, чем это выходит с обычной разводкой на подложке.

Цифры из заявки такие: мосты расширяют допустимую дистанцию с 6 мм до 16 мм. И это не просто «удлинитель». OpenAI описывает два сценария, когда мост берёт на себя часть логики:

- Функции контроллера HBM: часть управления стеком можно вынести в мост.

- Функции высокоскоростного PHY: мост может выступать как физический интерфейс связи между чиплетами в пакете.

Для die-to-die соединения в заявке упоминается соответствие UCIe (Universal Chiplet Interconnect Express). Это важная деталь: OpenAI явно смотрит в сторону «универсальных» чиплетных интерфейсов, а не закрытых шин.

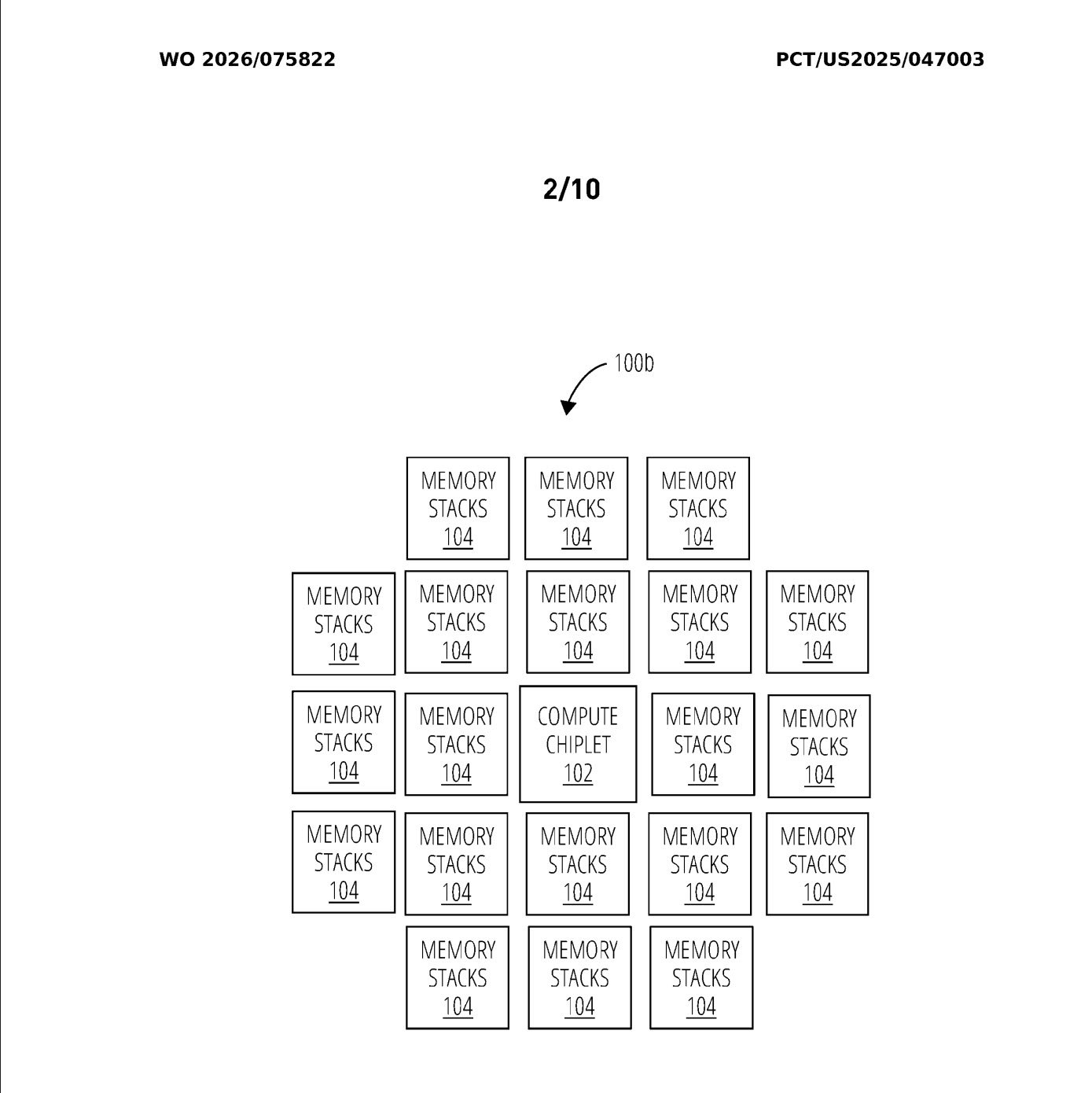

Пример из патента: один compute-чиплет и 20 HBM-стеков

Самая громкая иллюстрация из патента — пример, где один вычислительный чиплет окружён 20 HBM-стеками, подключёнными через Embedded Logic Bridges. В тексте заявки OpenAI прямо сравнивает это с «традиционным» потолком, где обычно говорят про 4/6/8 стеков.

Логика простая: больше HBM рядом с вычислением — выше суммарная ёмкость памяти, а значит крупные модели меньше упираются в дефицит памяти при обучении и инференсе. В заявке это описано как способ масштабировать память для AI и HPC-нагрузок, которым нужен быстрый доступ к большим объёмам данных.

Почему это похоже на Intel EMIB

В патенте OpenAI мосты описаны как embedded-решение для межчиплетных соединений. По смыслу это близко к Intel EMIB (Embedded Multi-Interconnect Bridge) — технологии упаковки, где маленькие «мостики» соединяют кристаллы без огромного интерпозера.

В описании упоминаются преимущества такого подхода, характерные и для EMIB-семейства: мосты маленькие, конструкция проще, можно выходить за ограничения ретикла интерпозеров, а стоимость потенциально ниже по сравнению с крупными интерпозерными решениями. Отдельно названа и эволюция технологии — EMIB-T.

Прямого заявления «OpenAI будет делать чип на Intel EMIB» в патенте нет. Но сама идея архитектурно ложится в ту же нишу, где EMIB уже существует как промышленная технология.

Патент OpenAI опубликован под названием “Non-Adjacent Connection of High-Bandwidth Memory Chiplets, I/O Chiplets, And Compute Chiplets Through Embedded Logic Bridges” — документ доступен в базе WIPO: WO2026075822.