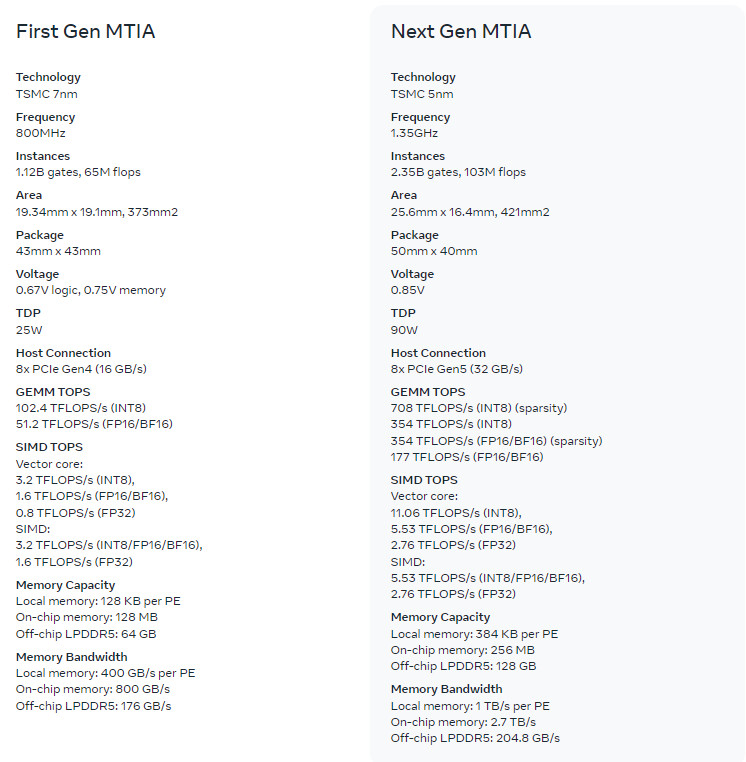

Компания Meta анонсировала новое поколение чипа Meta Training and Inference Accelerator (MTIA), разработанного для обучения и вывода моделей искусственного интеллекта. Новый чип MTIA, относящийся ко второму поколению специализированных микросхем Meta для ИИ, изготавливается с использованием 5-нм технологии TSMC. Работающий на частоте 1,35 ГГц, он потребляет 90 Вт TDP, что значительно больше по сравнению с 25 Вт у предыдущего поколения.

Чип отличается возможностью обработки с помощью базовых подпрограмм линейной алгебры (BLAS), включая умножение матриц и векторную/SIMD-обработку. В режиме обработки матриц GEMM каждый чип способен обрабатывать до 708 терафлопс при INT8 с разрежённостью и 354 терафлопс без неё, а также 354 терафлопс при FP16/BF16 с разрежённостью и 177 терафлопс без неё.

Классическая векторная обработка происходит медленнее: 11,06 терафлопс при INT8, 5,53 терафлопс при FP16/BF16 и 2,76 терафлопс при одинарной точности FP32. Чип MTIA создан исключительно для обучения и вывода ИИ на базе фреймворка PyTorch от Meta и открытого исходного кода бэкенда Triton, который оптимизирует производительность за счёт генерации кода компилятора. Meta применяет его для всех своих моделей Llama, и с предстоящим выпуском Llama3 эти чипы будут использоваться для их обучения.

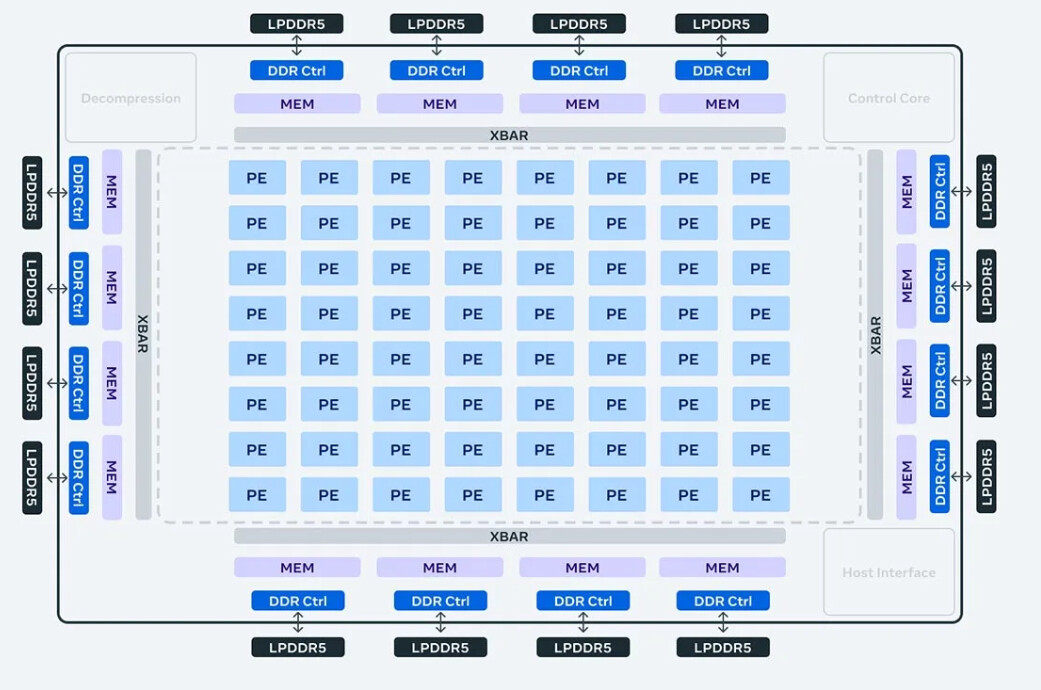

Для интеграции в систему Meta устанавливает два таких чипа на одной плате, сочетая их с 128 ГБ памяти LPDDR5. Плата подключается к системе через интерфейс PCIe Gen 5. При комбинации нескольких плат можно добиться теоретической производительности в 101,95 петафлопс.